About Me

I am a software engineer from the UK, working at Qualcomm (and Nuvia pre-acquisition) where amongst other things I’m responsible for pre-silicon software enablement covering application processor firmware, operating systems and virtual platforms on our custom CPU designs.

Prior to Nuvia/Qualcomm, I was the engineering team lead for Ksplice at Oracle which provides rebootless OS updates for Linux systems. I have a keen interest in CPU architecture and all things low-level. I have designed three CPU’s - a RISC-V RV32IMAZicsrZifencei core achieving 2.61 CoreMark/MHZ and booting mainline Linux, a x86 compatible and another home-grown 32-bit RISC, both with SoC reference designs.

Projects

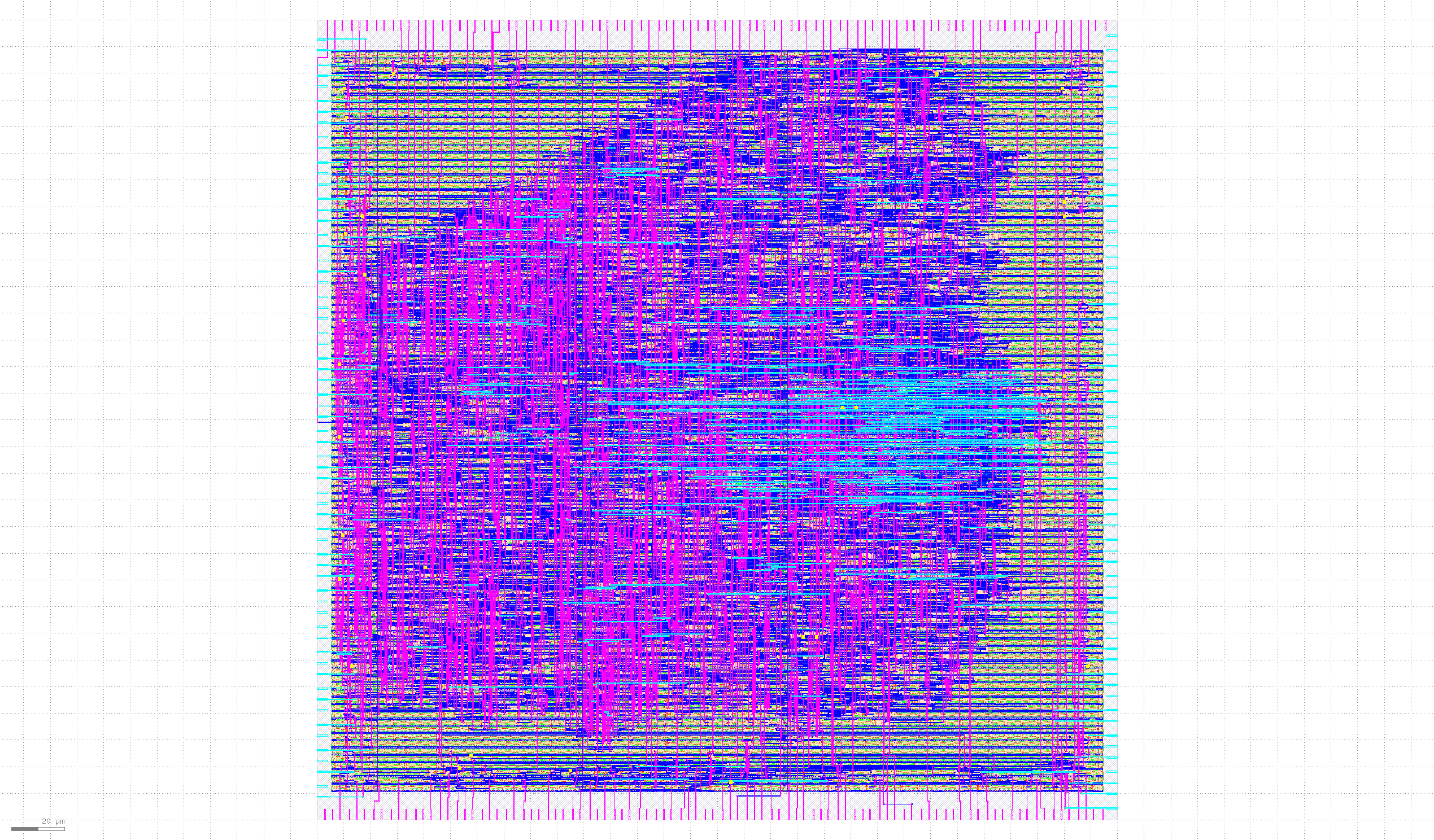

I have designed and built a number of CPU cores, most recently a RISC-V RV32IMA core that successfully runs mainline Linux with a CoreMark score of 2.61/MHz. The core is in-order with a 7 stage pipeline, out of order completion, register renaming, dynamic branch prediction and indirect branch target prediction, set-associative caches, fully associative TLBs and AXI4 support. A design for the Digilent Arty S7 board uses 32KB and 16 way TLB each for instruction and data paths. Externally, Xilinx IP provides AXI4 interconnect, SPI controller, interrupt controller, DDR3 controller and 16550A. I successfully hardened the core with OpenLane on the SKY130A process.

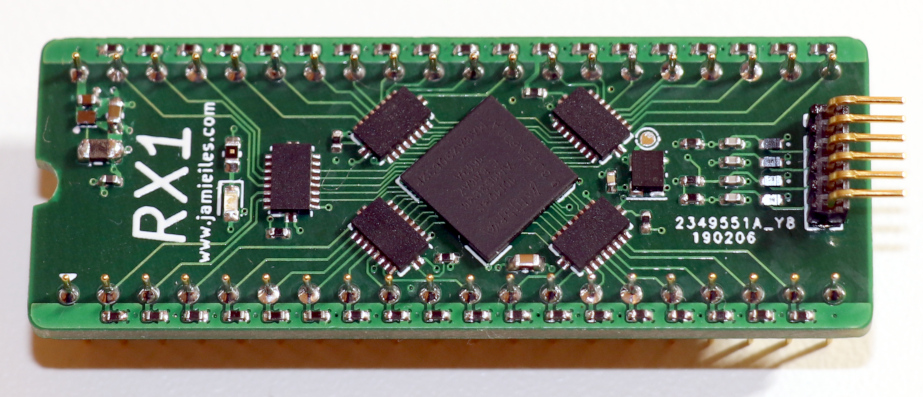

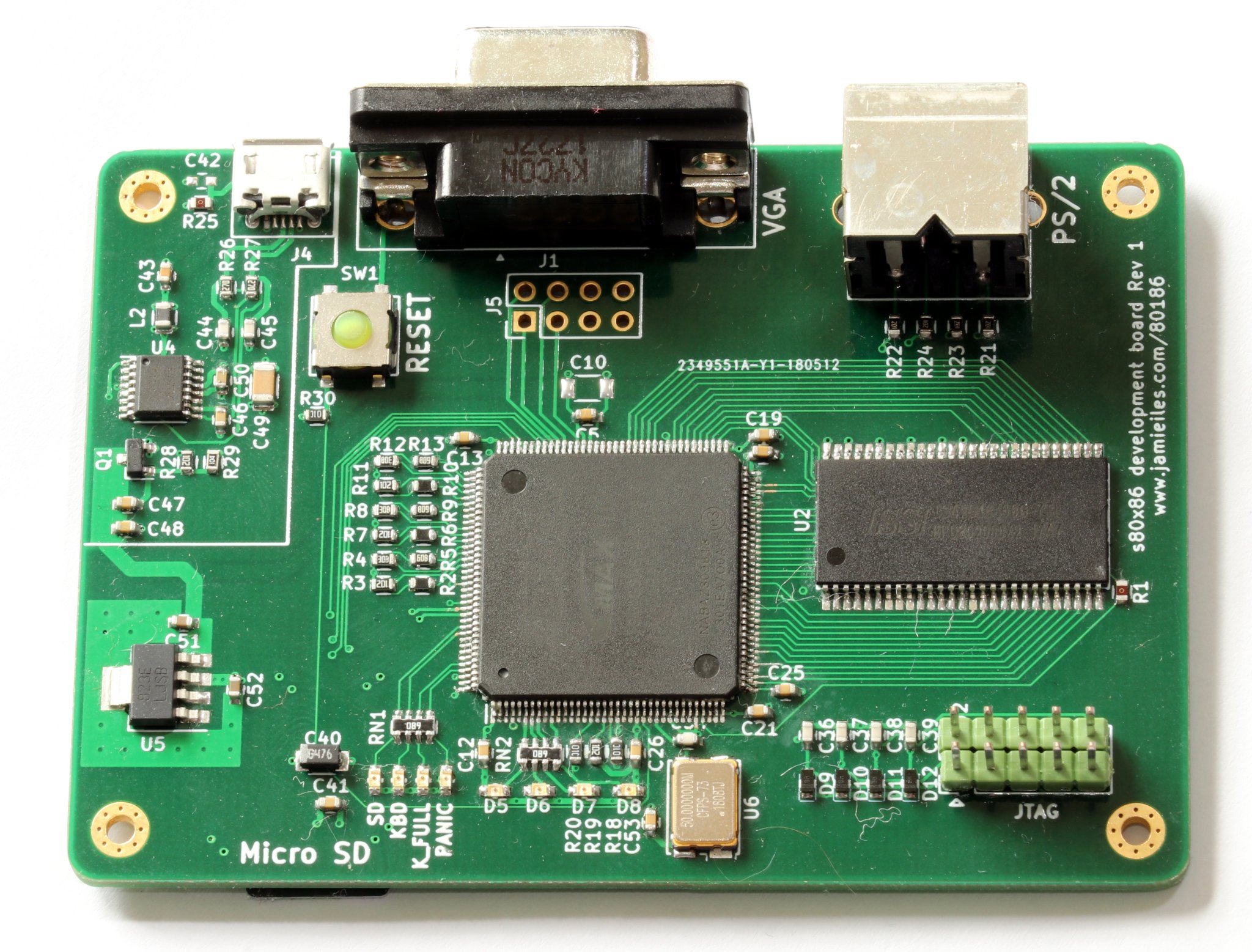

Previously, I created an 80186 compatible IP core from scratch which currently runs at 60MHz on a Cyclone V FPGA in ~1750 ALMs, implementing the full 80186 ISA, traps, faults + interrupts along with a JTAG TAP. The core has a comprehensive test suite using Verilator + Google Test, a C++ model to verify against, and a build system using CMake+Docker. A reference design includes an SDRAM controller, MCGA graphics, PS/2 keyboard+mouse controller, fixed disk emulation on an SD card, lightweight PIC+PIT implementations and a BIOS. The system can run a wide range of DOS based applications with good performance.

The Oldland CPU was my first home-grown CPU, a full-featured 32-bit RISC CPU, written in Verilog and synthesizable on FPGAs. The CPU features a 5 stage pipeline, privilege modes, caches, TLB’s and a debug controller. The SoC has an SDRAM controller, SPI master, UART, timers, interrupt controller and other peripherals. I have also ported binutils, gcc, newlib, u-boot and RTEMS to the Oldland architecture.

I have been experimenting with ASIC design after completing the ZeroToAsic course where I designed an A5/1 keystream generator for the PicoRV32 on the Caravel harness.

I have a number of github repositories including the s80x86 CPU, Oldland CPU, the picoxcell Linux kernel tree, some configuration files and a bunch of miscellaneous scripts and projects in progress. I have contributed to a number of popular open-source projects including Linux kernel, Verilator, qemu, RTEMS, Zephyr and others.

My Linux kernel contributions include ARM performance counters, the picoxcell family of ARM devices and associated drivers, support for device tree on ARM, and other bug fixes and driver improvements.

Take a look at my resume for professional experience.

Contact Details

email: jamie <at> jamieiles <dot> com

gpg: public key, fingerprint: C622 D8F8 26C1 A1F7 94F5 C53F C686 AD0A 9B42 49F5